This article is more than 1 year old

Xilinx to bust ACAP in the dome of data centres all over with uber FPGA

That's an Adaptive Compute Acceleration Platform btw

Xilinx is developing a monstrous FPGA that can be dynamically changed at the hardware level.

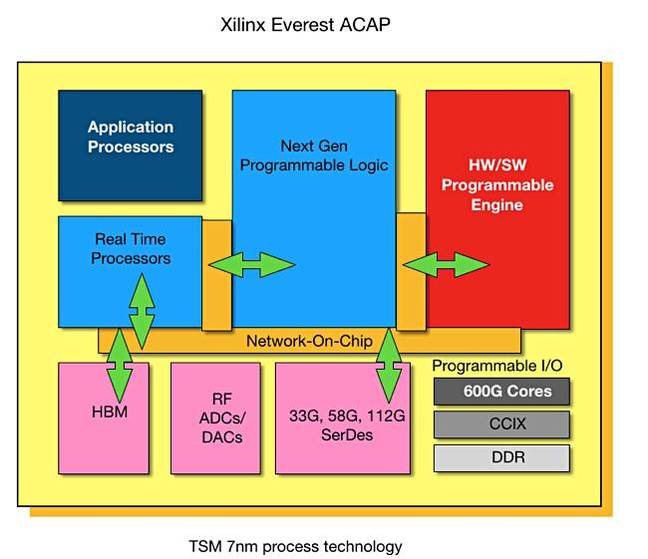

The biz's "Everest" project is the development of what Xilinx termed an Adaptive Compute Acceleration Platform (ACAP), an integrated multi-core heterogeneous design that goes way beyond your bog-standard FPGA, apparently. It is being built with TSMC's 7nm process technology and tapes out later this year.

Xilinx president and CEO Victor Peng, appointed January, claimed it is the "most significant engineering accomplishment since the invention of the FPGA".

The ACAP can be programmed at the RTL (Register-Transfer Level) with FPGA tools, and software devs can code for ACAP-based systems using C/C++, OpenCL and Python.

The Everest ACAP features up to 50 billion transistors and is said to provide:

- Distributed memory

- Hardware-programmable DSP blocks

- Multicore SoC

- One or more software-programmable, hardware-adaptable, compute engines

- Network on chip (NoC)

- On-chip control blocks for security and power management

- Hardware-programmable memory controller

- CCIX and PCIe support

- Multi-mode Ethernet controllers

- Programmable I/O interfaces and serialisation/deserialisation (SerDes)

- High-bandwidth memory or programmable ADCs and DACs in some versions

The idea is to accelerate a variety of compute workloads – financial risk modelling, personalised medicine, livestream events, IoT sensor analytics, AI speech services and screening social videos – and optimise the ACAP dynamically, in milliseconds, as workloads change.

Performance

It is expected to provide 20x the performance of Xilinx's 16nm Virtex VU9P FPGA product. The firm claimed Everest-based 5G remote radio heads will have 4x the bandwidth versus the latest 16nm-based radios. The performance per-watt efficiency is also claimed to be better, with a 10x improvement mentioned.

Xilinx claimed that in general Everest will be 10-100x faster than CPUs for new workloads, and cover more use cases than GPUs or ASICs.

And detailed performance claims from Xilinx show how serious it is about the Everest development.

Applications

Applications for the Everest ACAP are in the big data and AI areas: video transcoding, database, data compression, search, AI inference, genomics, machine vision, computational storage and network acceleration.

Anticipated markets include the automotive, industrial, scientific and medical, aerospace and defence, test, measurement and emulation, audio/video and broadcast, and consumer sectors.

This is a big deal for Xilinx. The company said 1,500 engineers are working on Everest, which has been in development for more than four years at a cost of $1bn. Some customers have had software tools delivered and product shipments should start in 2019, if all goes according to plan.

That's a year out and gives Intel's Altera crew time to respond, if the FPGA industry jungle drums haven't already alerted them.

Our sister publication, The Next Platform, has an in-depth report here. ®