This article is more than 1 year old

Intel hints at server processor plans for the rest of this year

New chippery all around, from tiny Atom to big bad Xeon E7

Back to the drawing board

Intel is also going back to the Centerton Atom drawing board and creating a version called "Briarwood" that's aimed specifically at storage devices. While the Centerton Atom S1200 chip had only eight lanes of PCI-Express 2.0 peripheral capacity, the Briarwood Atom S12X9 processors will have 40 lanes of PCI bandwidth.

Graff says that by putting more PCI-Express 2.0 lanes right on the Atom chip, companies building low-end storage arrays can now build their arrays without putting a PCI switch between the processor and the storage devices it controls. These switches list for around $137, according to Intel, and at high volumes they still cost around $20. That's $20 the storage vendor gets to keep.

The Atom S12X9 processors will also sport RAID acceleration features that allow for calculations for RAID 5 and 6 data-protection algorithms to be offloaded from the CPU cores. The storage-goosed Atoms will also have a feature called asynchronous DRAM refresh, which can put the contents of a write buffer and main memory into a self-refresh mode in the event of a power failure or when a processor or an operating system locks up. The DRAM memory has to have battery backup, of course, but in a storage device you never want to lose data in cache or main memory until you know it is placed on permanent media.

The Briarwood Atom for storage products will also have support for non-transparent bridging, which is a clustering technology that will allow two Briarwood Atoms to be linked over sixteen lanes of PCI-Express bus to each other in an active-active cluster that allows one node to fail but the storage array still keeps working.

The Briarwood Atom S12X9 chip is available now, by the way.

Intel is also hinting that it will make a special variant of the Atom S Series processor aimed at networking devices, called "Rangeley". No other details about the Rangeley Atom chip are being made available at IDF Beijing.

The Haswell Xeon E3 chip will come out about the same time as desktop and notebook versions

In the middle of this year, more or less concurrent with the desktop and notebook versions of the Haswell Core processors, Intel will kick out a Xeon E3 based on the Haswell design and aimed at single-socket machines.

The Haswell chips have a new, energy-efficient microarchitecture etched on the same 22nm processes as the Ivy Bridge family of PC and server chips. With the Ivy Bridge Xeon E3s, Intel could get a low-voltage part down to a 17-watt thermal design point, but with the Haswell Xeon E3, Intel will be pushing it down to 13 watts, thanks to the process shrink.

Like other Xeon E3s, some of the Haswell E3-1200 v3 variants will have integrated graphics, which some server makers are interested in for video transcoding, and workstation makers will use as well. And there will be other variants that have the integrated GPUs deactivated and a price-cut so a server can burn less juice and cost less dough.

The buzz on the street is that the Haswell Xeon E3s will sport four cores and clock from 2.5GHz to 3.6GHz, which is about the same speeds of the current Ivy Bridge Xeon E3-1200 v3 chips from May 2012.

It will be interesting to see how performance and performance per watt stack up between the v2 and v3 versions of the E3-1200 chips. And hopefully main memory will get bumped up to more than 32GB across four slots with the E3-1200 v3 chips, too. It would be good to see an integrated Ethernet controller on this chip, as well, but no one has said boo about that.

The workhorse Xeon E5 gets a refresh to Ivy Bridge in the third quarter

The Xeon E5 is not just getting a shrink from 32nm to 22nm that will allow it to burn less juice to do the same work, but the word on the street is that Intel will add two more cores to the E5-2600 v2 processor, boosting it from the eight cores with the Sandy Bridge-EP chips to ten cores with the Ivy Bridge-EPs. Graff did not confirm this in the briefing with El Reg, of course, and merely said what Bryant will say at IDF Beijing, which is that a 22nm Ivy Bridge-EP is in the works that will have "exceptional energy efficiency" and "best-in-class-performance."

Assuming the clock speeds remain about the same as the Xeon E5-2600s launched in March 2012, which was between 1.8GHz and 2.9GHz, that should mean about a 25 per cent performance boost with the move to ten cores. Jumping from 20MB of L3 cache with the Sandy Bridge parts to 30MB with the Ivy Bridge parts will boost performance even further. How much is hard to say because cache use is so workload-dependent. For some jobs, that extra 10MB of cache will make a big difference. That we know for sure.

After skipping Sandy Bridge, Intel will get a Xeon E7 out based on Ivy Bridge

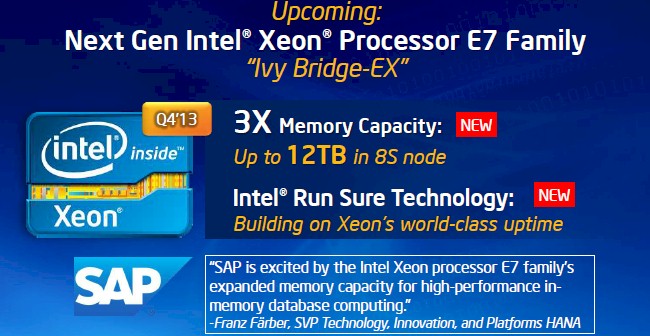

Customers using high-end Xeon E7 processors to build large-memory systems with four or eight sockets are going to get some a needed performance boost in the fourth quarter of this year with a new Xeon E7 based on the "Ivy Bridge-EX" design.

Intel skipped the Sandy Bridge-EX chip last year, giving server makers more time to sell existing "Westmere-EX" Xeon E7-2800 (two-socket), E7-4800 (four-socket), and E7-8800 machines without having to absorb a new socket and system design. The Ivy Bridge-EX will use the same socket that the Sandy Bridge-EX would have used, and it is not socket-compatible with the current Xeon E7 machines.

Ah, but will Intel call them the Xeon E7 v2 or v3 chips? Technically they are v3 chips, even if you can't have v2. We'll call them Xeon E7 v3 processors just to avoid confusion.

The word on the street is that the Xeon E7 v3 chips will sport 15 cores, but that sounds silly. The current Xeon E7 v1 processors have ten cores, and it seems likely that the v2 chips were due to have 12 cores if you look at the die shot of the Xeon E7 v1s.

Back when the Xeon E7 v1 chips were previewing in February 2011 at the ISSCC chip extravaganza, El Reg showed you that it was a twelve-core design with two of the bottom cores on the die lopped off.

The Westmere Xeon E7 chip was already in a 32nm process, so to add those cores back with Sandy Bridge, Intel would either have to make the chip bigger and put it in a different socket or move it to 22nm, which is the process used for Ivy Bridge parts. Intel clearly doesn't want an Ivy Bridge part coming out on 14nm two years from now, now with SAP trying to build HANA in-memory appliances on Xeon E7 chips.

So with the Xeon E7 v3 chips, the Ivy Bridge chip is being implemented in 22nm and coming out about when you would expect it to. As for the core count, 12, 14, and maybe 16 make sense. But 15 does not make a lot of sense – unless the Run Sure Technology that Intel is giving a name to as a feature in the future Xeon E7 v3 chips is actually a hot-spare chip to provide even better reliability than Xeons currently do.

It seems far more likely that the Xeon E7 v3 is a 16-core design with one core only enabled as a hot spare than the chip having literally 15 cores on the die. That would screw up the symmetry in the caches and the rings that connect the cores and caches together.

The only other thing that Intel is saying about the future Xeon E7 v3 chips is that they will have three times the memory capacity of the current Xeon E7 v1 processors. That means an eight-socket box will be able to scale up to 12TB of main memory. ®