Original URL: https://www.theregister.com/2011/12/07/suvolta_ddc_transistor/

BREAKTHROUGH: Feisty startup slashes chip power by 50%

SuVolta to Intel: 'The future is the $10 chip, not the $200 chip'

Posted in Personal Tech, 7th December 2011 22:29 GMT

An impressively staffed startup by the name of SuVolta has teamed up with Japanese heavyweight Fujitsu Semiconductor to create a new chip-baking technique that promises low-power, inexpensive chips created in a highly scalable process and manufactured using equipment that's already ready in chip foundries.

Yes, that description is a bit of a mouthful – but that's the breadth of promise offered by SuVolta's "deeply depleted channel" (DDC) CMOS transistor tech, as presented on Wednesday by a Fujitsu researcher at the 2011 International Electron Devices Meeting (IEDM) currently underway in Washington DC.

If DDC works as advertised – and from the deep-dive details and test results provided to The Reg by SuVolta's director of device and modeling Lucian Shifren, we have no reason to think that it shouldn't – it could revolutionize how low-power system-on-chip (SoC) silicon is created.

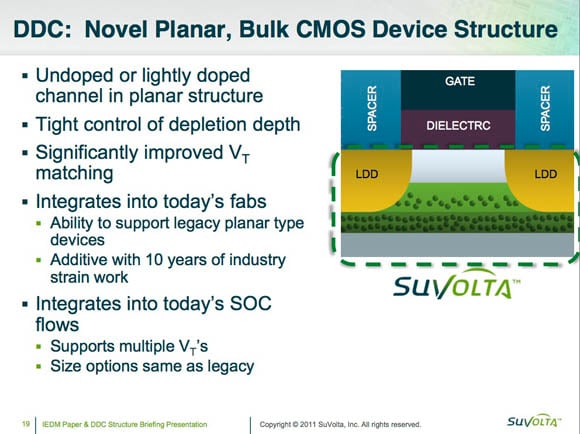

What DDC involves, and what provides its promise, is a new way of creating transistors based on standard bulk planar CMOS manufacturing techniques, and not on more-expensive and specialized transistor manufacturing processes that have cropped up in the past decade or so to allow chip designers to keep pace with that tough taskmaster, Moore's Law.

Shifren emphasized that although DDC could be applied to any level of chippery, SuVolta is currently more concerned with foundry-created, low-power chips, and not the hefty x86 CPUs baked by Intel in their custom fabs. SoCs are where the market is headed, he told us.

"CPUs and GPUs are not actually driving the semiconductor market anymore," Shifren said. "What's driving it are SoCs, and especially those adapted to mobile forms."

The company that's currently driving semiconductor technology, however, is Intel. But Chipzilla has traditionally focused its research on larger, more powerful chips based on the aging IA architecture – although it would dearly love to break into the lucrative mobile market, dominated by non-IA ARM chippery.

"If you look at the industry as a whole right now, who really defines the technology and the technology roadmap?" Shifren asked, rhetorically. "It's Intel." He also gave historical props to IBM, but averred that in recent years Intel has been leading the way.

As an example, Shifren offered Intel's variation of 3D FinFET transistor technology, what Chipzilla calls Tri-Gate. "Have a look at how after Intel made its announcement of FinFET, everybody and their mother came out and said they were going to be working on FinFET," he said.

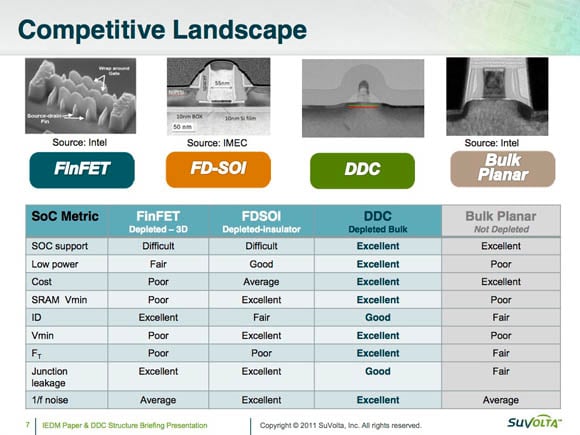

According to Shifren, however, neither FinFET nor another transistor structure known as fully depleted silicon-on-insulator (FD-SOI), which has been around for nearly a decade, are the best choices for the low-power, low-cost SoC market – although others may disagree when Shifren says "I believe FD-SOI is dead."

SuVolta's DDC transistor shares many advantages of cheap-as-dirt, versatile bulk planar CMOS (click to enlarge)

Not only are both of those techniques expensive when compared with good ol' traditional non-depleted planar bulk CMOS, Shifren says, but they don't scale well for creating a range of chips running at different voltages.

(A bit of background: you'll notice that the term "depleted" is being bandied about a bit. Simply put, a depleted transistor is one in which stray current is minimized in such a way as to prevent power leakage, and to allow the transistor to be activated at a lower voltage. For a fuller explanation, check out an earlier Reg article about Intel's tri-gate transistors.)

Shifren told us that voltage reduction has been given short shrift in the drive to keep up with Moore's Law. "If you look at Moore's Law, and how Moore's Law has been evolving over the last couple of years," he said, "advances in patterning and moving to double patterning, immersion masks, and things like that, the industry has been able to keep along with Moore's Law – as long as you're talking about dimensional scaling.

"But if you have a look at the voltages," he continued, "they haven't scaled nearly as quickly. They actually haven't scaled at all in the last couple of years."

He recited the history of processor voltage scaling, starting a five volts, then down to the low fours, then 3.5V, 2.5V, 1.8V. Then curve of the decreases began to flatten out, now hovering around 1V to 0.7V. Moore's Law, on the other hand, has kept chugging along, doubling transistor density every 18 to 24 months.

SuVolta's breakthrough is that it has managed to slash that voltage requirement essentially in half, a level of improvement that should please any fan of Moore's Law–scale improvements. The company's DDC transistors, used in a proof-of-concept SRAM chip manufactured by Fujitsu, require a mere 0.425V.

Three layers, no waiting

Another major transistor bugaboo is voltage variability – and from SuVolta's point of view, taming variability is the key to lower voltages. It doesn't take a PhD chip boffin to understand that the lower the variability in a transistor's operating voltage, the lower the overall voltage supplied to a million-transistor chip needs to be to ensure that all the transistors will fire up when asked to.

Since reducing a chip's operating voltage is key to reducing its overall power consumption – along with other niceties such as intelligent power managment and the like – Shifren and the SuVolta team focused on developing a transistor that could operate at low, steady voltages and still be manufacturable in existing fabs with very little equipment modification.

One sticking point, however, was that SuVolta wanted to build a transistor that could be operated at multiple voltages. Foundries, after all, have customers with different needs – unlike Intel, which builds its own chips in its own fabs, and thus has less of a need for the ability to create chips that operate at a broad range of voltages.

What SuVolta came up with was a new way of building a transistor's channel – its pathway for current – that cut its voltage variablity nearly in half, thus allowing the overall voltage to be lowered, and that permitted the manufacturing process to create a broad range of transistors at a broad range of voltages.

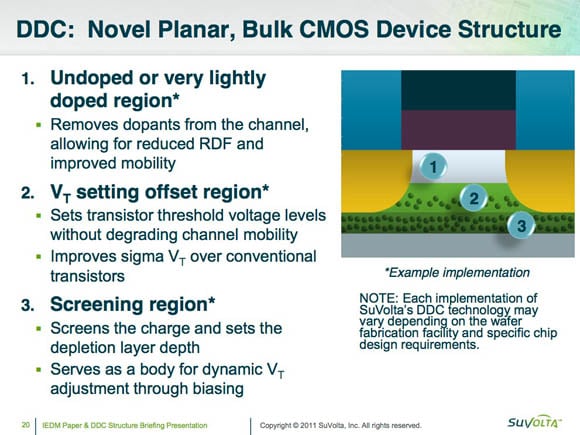

A DDC transistor's channel is a three-layer parfait. The layer in direct contact with the transistor's gate, or on-off switch, is undoped or very lightly doped silicon. The lack of dopants (impurities added to increase conductivity) in this layer avoids the dreaded volage-variability-inducing random dopant fluctuation (RDF), as well as allowing the channel to be highly depleted.

A second layer beneath the no-or-low dopant layer sets the transistor's "it's time to turn on now" threshold voltage (VT), which allows the DDC transistor to meet its objective of being fabricated with a broad range of voltage requirements. This is accomplished by adding a medium dose of dopants that control the voltage properties of the first channel.

"By changing the dose in that layer," Shifren says, "we're able to apply a potential to the channel non-locally, from underneath the channel. So instead of applying the potential in between the source and the drain, or within the channel, we actually apply it from underneath using layer number two."

Although Shifren admits that VT variations increase when the second channel cranks up the first channel to a higher VT, "it's significantly less than if we put all that dose into the [first] channel."

The third layer – which SuVolta calls the "screening region" – is more highly doped layer that terminates the depletion depth. "You don't want your depletion depth going way too deep into the device," Shifren says. A secure termination of the depletion depth assures that the DDC exhibits fully depleted behavior.

"The reason why people do FinFET or FD-SOI is to have that depleted behavior, and this allows us to have that depleted behavior," Shifren told us.

The other advantage of the third layer's termination of the depletion region brings us back to the goal of reducing VT variability. "That depletion region is going to be very uniform across the entire part, and it's this uniformity that helps us to achieve the excellent sigma VT" Shifren said, referring to DDC's low standard deviation of all of a chip's transistors' threshold voltages (σVT).

If, by the way, all this doping, depletion, and deviation is not quite geeky enough for you, you can find a more complete explanation in SuVolta's technology brief, "Transistor VT Variation, VDD Scaling, and Leakage Power". Knock yourself out.

By now, you may very well be asking, "What's in it for me?" Fair question.

Should SuVolta's DDC transistor prove as impressive in reality as it is on paper, its 50 per cent decrease in voltage variation should enable a concomitant 30 per cent reduction in power supply voltage. Simply put, a lower power supply voltage means less power needed, less power needed means longer battery life in your mobile devices.

Also, Shifren assured us that creating DDC-transistor chips won't require expensive foundry retooling and process-flow changes, but instead minor tweaks to existing bulk planar CMOS chip-baking tools and techniques. Cheap manufacturing means cheap chips, and cheap chips means cheap consumer-electronics gadgets and gizmos

Finally, although stuffing servers with cheap chips based on DDC transistors could also help massive data centers reduce their power bills, at this point in time SuVolta is aiming at the mobile SoC market.

"The market's now moving to a point where you're really going to be driven by the $10 chip and not the $200 chip," Shifren told us, "so these fancy 3D technologies and FD-SOI products, they're going to be too expensive for where the market is going."

If SuVolta's work with Fujitsu pans out, Intel's "fancy 3D technology", tri-gate, might have a strong competitor facing it at the low end of the market – a place where Chipzilla has yet to find success. ®