Original URL: https://www.theregister.com/2011/05/10/tilera_tilegx_8000_chips/

Tilera preps 100-core chips for network gear

Massively multicore server chips loom

Posted in Channel, 10th May 2011 06:00 GMT

Upstart multicore chip maker Tilera is using the Interop networking trade show as the coming out party for its long-awaited Tile-Gx series of processors, which top out at 100 cores on a single die.

The company is rolling out the Tile-Gx processors, which it first revealed back in October 2009, at Interop in Las Vegas this week because the first instantiation of the Tile-Gx chips that is coming out the door is aimed specifically at the network equipment makers who have been early adopters of the Tilera chips.

Tilera is changing to a three-prong attack on the chip racket with its third generation of chips, Troy Bailey, vice president of marketing at the chip maker, tells El Reg. Rather than make one set of processors aimed at all potential customers, as it did with its first-generation Tile64 and second-generation TilePro chips, Tilera is going to offer three different families of Tile-Gx chips aimed at three different customers: the Tile-Gx 8000 series for network equipment makers, the Tile-Gx 5000 series for multimedia appliances, and the Tile-Gx 3000 series for hyper-efficient servers.

"Rather than having one-size-fits-all, we now have different style of products," explains Bailey. "Some applications need a lot of memory or I/O, and other applications do not need it."

It is not clear if Tilera is actually going to fab three different flavors of the chips – and Bailey was not at liberty to say – but given how expensive it is to design and test chips, it is safe to assume that what Tilera is really doing is being smart about Tile-Gx chips as they come off of Taiwan Semiconductor Manufacturing Corp's 40 nanometer fabs. There really are four different Tile-Gx chips – squares with 16, 36, 64, and 100 cores as well as different amounts of on-chip system components. That is enough variation to have to pay TSMC for.

So it stands to reason that what Tilera is doing is using partial duds where there is a booger on a crypto unit or a memory controller or what have you for a workload, such as a server, which may not need as many or none of these components. This is the way all processor makers "improve" their chip yields, and Tilera, having packed so many components on its system-on-chip designs and aiming at three different markets, can take it to extremes. As it is with core counts.

The Tile-Gx design has a mesh network linking all of the cores together as well as linking the 256KB L2 caches per core into a single coherent L3 cache. Each core also has 32KB of L1 data cache and 32KB of L1 instruction cache. So on the 100-core variant of the chip, there is 32MB of total cache for the data to frolic within. It is widely believed that the Tilera cores are based on a licensed version of the MIPS core, with the third-generation Tile-Gx chips sporting 64-bit processing but only 40-bit memory addressing, Bailey revealed to El Reg. That means the top-end part can address up to 1TB of DDR3 main memory, and interestingly, the Tilera processors will be able to run that memory faster than their cores, unlike most other processors.

The Tile-Gx chips also have additional SIMD instructions that make use of a four multiplier-accumulator (MAC) per cycle unit that can deliver 600 billion MACs per second, which Tilera says is 12 times the fastest digital signal processor on the market when the design was launched in late 2009. The chips also have two MiCA engines, short for Multistream iMesh Crypto Acelerators, and are able to deliver 40 Gb/sec of bandwidth on cryptographic work and 20 Gb/sec on compression and decompression jobs.

The chip also includes a packet processing accelerator that sits between the cores and the on-chip network interfaces called mPIPE, short for multicore programmable intelligent packet engine), which does load balancing between the cores and the network interfaces.

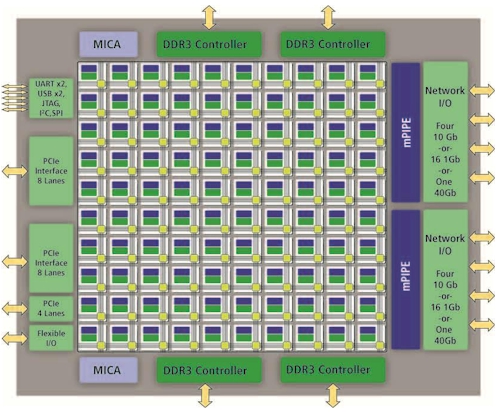

The 100-core variant of the chip is a 10x10 grid of cores all linked by the iMesh. Four memory controllers are along the top and bottom edges (two on top, and two on the bottom). The MiCA crypto units are in the left-hand corners, and three PCI-Express 2.0 I/O processors (two eight-land and one four-lane) and various I/O controllers are there, too. (With a total of 80 Gb/sec of PCI-Express I/O bandwidth). The right-hand side of the chip has eight XAUI ports that can be configured as a total of 32 Gigabit Ethernet ports or eight 10 Gigabit Ethernet ports. Because everything needed in the system is on the Tile chip, there is no northbridge or southbridge chipset. It is a very elegant design.

Package rethink

Tilera was expecting to get a 36-core and 16-core Tile-Gx chip out the door in the fourth quarter of last year, with the 100-core variant due in the first quarter and the 64-core variant due a few months later. That obviously didn't happen and Tilera has used the time to rethink how it is packaging up and selling its chips. The reason for the delay has not been explained, and Bailey says that the Tile-Gx family for network gear will sample in July and be in production shortly after that. These chips are expected to be used in intrusion prevention and detection, firewall, virtual private networking, WAN optimization, network monitoring, and other kinds of equipment.

The Tilera stack includes a custom Linux compiler and parallel programming environment, as well as Apache, MySQL, Perl, PHP, and other expected open source tools.

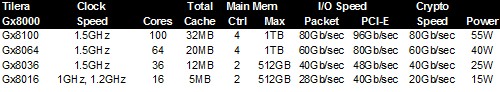

There are four different Tile-Gx 8000 series processors aimed at network equipment makers, as shown below:

Back in late 2009, Tilera was guessing that a 100-core Tile-Gx chip would cost around $1,000 while a 36-core version would cost around $400, but with the new packaging, anything is possible. Bailey said that pricing was not going to be disclosed since the chips were not even sampling yet.

Bailey did tell El Reg that the Tile-Gx 3000 server version of the chips "will not be far behind" the Tile-Gx 8000 series. The server variants will likely not have all of the crypto units or Ethernet connectivity as the networking versions, but will probably have all the cores and memory controllers. The Tile-Gx 5000 chips will focus more on computing oomph and less on I/O, since they will be aimed at video conferencing, media steaming, media transcoding, and media gateway jobs. Bailey did not want to pre-announce these chips and said more information on the Tile-Gx 3000 and 5000 series would be available late in the second quarter.

With the Tile-Gx 3000 series, Tilera says that companies will be able to put about 20,000 cores in a standard server rack, and with the future 200-core "Stratton" kickers due in 2013 using TSMC's 28 nanometer wafer baking processes, it can double that up to 40,000 cores per rack. ®