This article is more than 1 year old

Third NAND dimension makes quad bit bucket cells feasible

A view on quad-level cell flash error correction

Analysis Error-checking code use is so much easier with 3D NAND than previous planar NAND that capacity-lifting quad-level cell technology becomes more feasible.

The use of error-checking code (ECC) technology involves adding redundancy to stored data by using an algorithm to work out how many bits to add and use. Block codes work on fixed-size blocks and Reed-Solomon coding is an example of this. It can detect more errors than it can correct.

Low-density parity-check (LDPC) codes are a newer version of ECC technology. BCH (Bose-Chaudhuri-Hocquenghem) codes are another. Binary BCH codes can be designed to correct multiple bit errors. Generally, the higher the number of bits you want to be able to correct, the more redundant ECC bits you have to add to data.

ECC is needed with NAND flash because reading cells does not provide a clearcut one or zero, and so the value if a byte or bytes can be distorted by errors.

Such errors can be detected and corrected with ECC codes.

As the reading difficulty of NAND increases, so too does the number of ECC bits you need to add and also the sophistication of the ECC algorithm. "Reading difficulty" is a loose way of saying that cell readability decreases as cell sizes get smaller and the number of bits it stores increases.

For example, with small cells there can be a cross-cell effect such that setting a value in one cell can cause contamination of the setting in an adjacent cell. These settings involve electrons – their number and stability decrease as cell sizes shrink.

Thus, inherently, MLC (2bits/cell) and TLC (3bits/cell) flash is harder to read than SLC (1bit/cell). While QLC (4bits/cell) is technically feasible, it has not been practical, until now, because cell readability is so difficult and the ECC codes and algorithms needed are too complex.

SanDisk tried to produce QLC NAND, using 43nm geometry planar construction, in 2009, but it gave up after a year or so.

In the same way, 20nm MLC flash cells are harder to read than 25nm cells and also than 35nm ones, and 16nm MLC flash cells are harder to read again. At this level, BCH and LDPC ECC technology is used for ECC.

A briefing document by Jim Handy from Objective Analysis says things get easier with 3D NAND.

There are two main reasons.

The first is that when 3D NAND flash chips were built, the cell size reverted back to around 40nm from the 15nm or so then being used in state-of-the-art 2D or planar NAND.

The second is that, due to the way 3D NAND is constructed, "the 3D NAND's floating gate or charge trap forms a circle around the pillar that serves as the channel, increasing its area by another 3+ times. A gate on today's 3D NAND chips is roughly equivalent to that of a 90nm planar NAND chip."

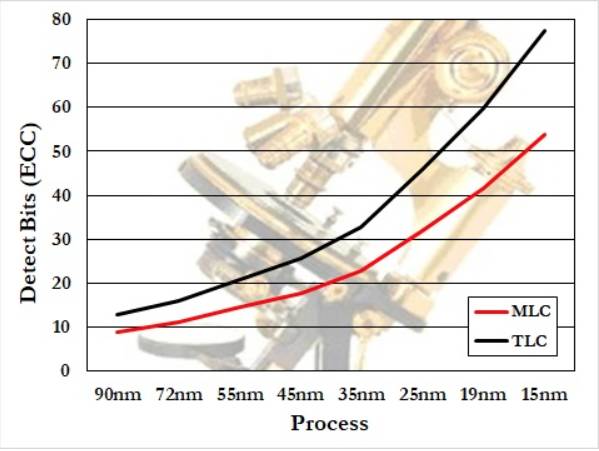

He provides a chart showing the number of ECC bits typically needed at various cell sizes for both MLC and TLC flash:

Whereas more than 75 bits are needed at a 15nm process geometry or cell size with TLC NAND, less than 15 are needed with a 90nm geometry.

Handy writes: "We can infer that fewer than 20 bits will be necessary for QLC 3D NAND. This is why QLC appears far more practical for 3D NAND than it ever was for planar NAND."

He raises the prospect of even having more bits per cell. "Over the long term I would assume that LDPC will be used in most 3D NAND controllers to allow even more than 4 bits to be stored per cell, but it may take some time to get to that point. During the near term it's reasonable to expect for 3D NAND to largely shift to QLC using simple BCH algorithms."

Imagine 5 bits/cell flash – pentadruple-level cell or PLC flash? We can't call it quintuple level cell because QLC is already used for quad-level cell flash. That would be a 25 per cent increase over QLC flash, 5 bits instead of 4. So a 1TB QLC SSD would become a 1.25TB PLC SSD. Mmm, tasty, but still several years away, if it happens at all.

For now QLC flash looks a little more realistic, and we might get a sniff of it some time towards the end of this year. ®