This article is more than 1 year old

IBM opens Power8 kimono (a little bit more)

Wafer baked in 22 nanometers

Last May El Reg gave you the little information we were able to gather on the impending Power7+ and future Power8 processor designs and their possible announcement dates in Power Systems machines.

Data was a little thin, and intentionally so on the part of Big Blue. But with Oracle kicking up a big fuss over Intel's Itanium processor roadmap - which the software giant says is a dead end - it looks like IBM has decided it was time to be more specific.

Only a little bit more specific, mind you. Server makers and chip makers don't like to make promises because business conditions change and issues crop up in reality that can cause a processor or server design and its schedule to diverge from the roadmap.

A case in point is one of the earlier schedules for the Power processor lineup, which had Power6 coming out in 2006, Power6+ in 2007, Power7 in 2008, and Power7+ in 2009. That was a two-year cadence for a new processor design and a two-year cadence for a chip manufacturing process shrink interwoven.

For reasons that IBM never explained, and which no doubt had to do with its wafer baking plant in East Fishkill, New York, and maybe its 65 nanometer processes as well as reduced competition from Intel and Sun Microsystems (now part of Oracle) in the high-end server racket, Big Blue lengthened the cadence by 50 per cent ahead of the Power6 launch. Also the Power6+ was not whatever it was supposed to be.

Power(6+) failure?

Our guess is Power6+ was supposed to be a quad-core chip, perhaps implemented in a 45 nanometer process, but it was nothing to write home about. (In fact, IBM tried to pretend that Power6+ chips, which had a few new instructions and a modest speed bump, were actually Power6 chips to avoid talking about whatever had gone wrong.)

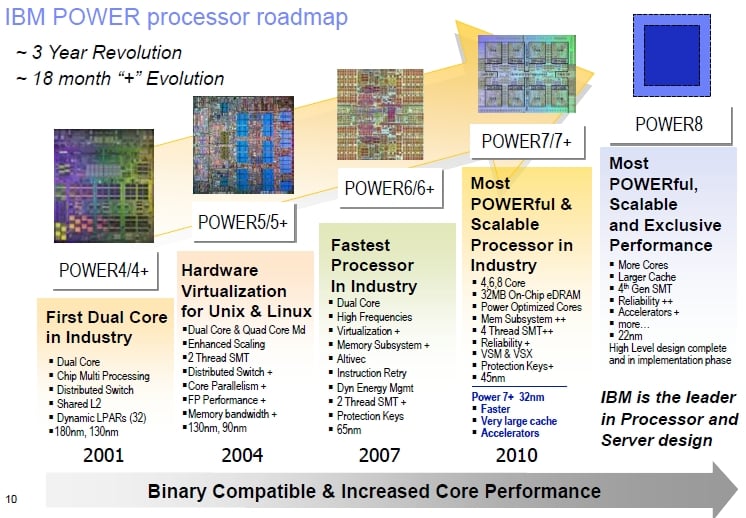

With the Power7 chip, IBM has committed to a three-year cadence for major processor designs and is back to using a process shrink halfway through the cycle with a modest design change. This is what IBM calls a 36-month "revolution" with an 18-month "+ evolution" embedded in the Power roadmap, and it is analogous to Intel's "tick-tock" meter with Core desktop and Xeon server processor launches.

In May we asked Steve Sibley, director of product management for the Power Systems line, if there would be a Power7+ processor; he confirmed that indeed there would be one.

The Power7+ chips will be socket-compatible with the Power7s, although IBM is making unspecified I/O enhancements to the chips that will require that customers move to Power7+ system boards to make use of them.

My guess is that the embedded InfiniBand that IBM uses to link to remote I/O drawers will be goosed (perhaps to 40Gb/sec QDR or 56Gb/sec FDR InfiniBand from the current 20Gb/sec DDR InfiniBand) and the system boards and/or chips will sport PCI-Express 3.0 peripheral controllers. At the time, we suggested that IBM would strongly want to use 32 nanometer processes on the Power7+ and use the shrink to crank the clocks.

As you can see from the latest Power roadmap, that looks to be the plan:

In the latest roadmap, IBM shows that the Power7+ chip will indeed use a 32 nanometer process, down significantly from the 45 nanometer process used with the Power7 chips that first came to market in February 2010 and were rolled up and down the Power Systems line through August of last year.

The updated roadmap says that the Power7+ chips will run faster, and will include a "very large cache" and "accelerators." Of course, the Power7 chips already have a 32MB on-chip L3 cache implemented in embedded DRAM.

My guess is the shrink to 32 nanometer will allow IBM to crank the clocks on the processors by 25-30 per cent. IBM could boost the eDRAM cache size, but that may require a lot of redesign work, and the whole point of the "evolution" part of the cycle is to not mess with the design too much. It is almost certain that IBM will stick with four, six, and eight core variants with the Power7+ chips.

I know what you are thinking: 18 months after February 2010 is August 2011, and last time I looked at my calendar, it was August 2011. But then again, I think the original plan was to get the initial Power7 machines out the door in April 2010 for May delivery, not February, which should put the Power7+ launch in October or November.

That should more or less coincide with Intel's "Sandy Bridge" Xeon E5 processor launch, which is slated for the fourth quarter. IBM originally planned to start with the Power 750 and Power 770 in April 2010 and the Power 720 and PS7XX blades and high-end Power 795 in October 2010.

IBM widened the product line considerably and also pulled the announcements forward by several months to catch the recovery wave from the Great Recession and to get its launches in phase with X64 processor launches from Advanced Micro Devices and Intel.

And what of Power8?

The previous external roadmap I got my hands from inside IBM didn't say much about the Power8 processor - which we should expect in the spring of 2013 or so - except that it was in the "concept phase." The latest roadmap sheds some light on what IBM's chip designers have cooking.

We can tell you that with the Power8 chip IBM is skipping a 28 nanometer process and jumping right to 22 nanometers, and that the high-level design for the chip is complete and in the implementation phase (where the kinks are being worked out in the design and the manufacturing processes).

IBM's roadmap says the Power8 chip will have more cores, larger caches, more accelerators than the Power7 and Power7+ chips as well as a fourth generation of the company's simultaneous multithreading (SMT).

It is a mystery how many cores IBM will put on the Power8 chip, but the shrink from 45 nanometer to 22 nanometer processes should allow for as many as 16 cores to be on a single Power8 chip - depending on the cache size and desired clock speed, of course.

IBM could try to crank clocks a little more and cut back to a dozen cores and fatter caches, depending on how it thinks the typical AIX and IBM i workload will make use of the cores. A Power8 system should offer roughly twice the oomph of a Power7 machine in the same class, socket for socket. ®