This article is more than 1 year old

Tilera throws gauntlet at Intel's feet

36-core Tile-Gx server chip crosses Sandy Bridge

Sampling in July

The Tile-Gx 3036 chip will be sampling in July – and yes, Chinese server maker Quanta is one of the early OEMs getting access to these chips. This 36-core chip will have a total of 12MB of cache on the die, with 66Tb/sec of iMesh bandwidth across the 6x6 grid of cores and 200 Gb/sec of memory bandwidth across its two DDR3 memory controllers.

The Tile-Gx 3036 supports up to 512GB of memory, and delivers 48Gb/sec of bandwidth across its two PCI-Express 2.0 ports (one x8 and one x4). Bishara says that Tilera expects to see Tile-Gx 3036 processors appear in products by the end of the year.

The 64-core and 100-core variants of the Tile-Gx 3000 series implement their cores in 8 x 8 and 10 x 10 grids and scale up the DDR3 memory controllers and PCI-Express 2.0 lanes accordingly. The Tile-Gx 3064 and 3100 processors will sample in early 2012 and will appear in products about six months later if all goes according to plan.

Because it is using a non-x64 instruction set, the Tilera chip requires its own variant of the Linux stack, which Tilera has put together. Specifically, Tilera has taken a CentOS-compatible Linux stack with the Linux 2.6.36 kernel and over 2,000 RPM packages to create its own Linux. (Yes, that is an authentic replica of an exact duplicate.)

The current development tool chain includes ANSI-compliant C and C++ as well as PHP, and Tilera's software engineers are putting the final touches on tuning up the Just-In-Time (JIT) compiler for its Java stack, which is important for customers wanting to run Hadoop and other big-data crunchers on Tilera-based machines.

The stack will also support the Erlang language created by Ericsson, which is significant because the Couchbase NoSQL database is written in a combination of C and Erlang. Couchbase running on Tilera servers will be demonstrated at Structure this week, and the company has already shown off memcached (written in C and C++) and Hadoop (written in Java) back in March.

Tilera vs Xeon

So how does the Tile-Gx 3000 stack up?

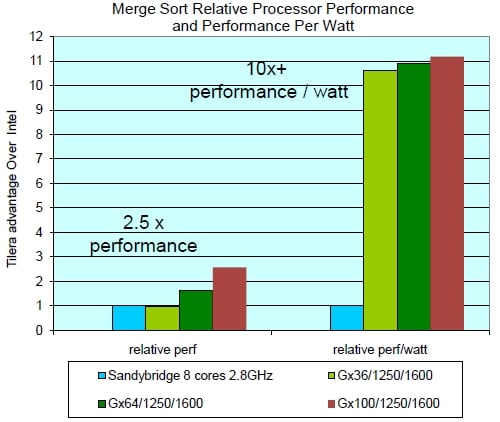

To give a sense of that, Tilera ran a merge/sort benchmark on its three variants of its Tile-Gx 3000 processors and also on an as-yet-unannounced eight-core "Sandy Bridge" Xeon E5 processor.

This benchmark was done at the behest of an unnamed storage company that is pitting the Tilera chips against Xeons. The Tile-Gx 3000s stack up pretty well in terms of performance and performance per watt, as you can see:

How the Tile GX-3000s stack up against Intel's Sandy Bridge

The 36-core chip stood toe-to-toe with the Xeon E5 running at 2.8GHz on the merge/sort benchmark, and the 64-core version did about 1.75 times the work and the 100-core version could do about 2.5 times the work. (This chart shows the old names of the Tile-Gx processors before they were broken into the 3000, 5000, and 8000 series.)

Perhaps more significantly, the Tilera chips just put the Xeon processors to shame on thermal efficiency, being able to do the work at ten times the efficiency per unit of work.

As you might imagine, Tilera wants to charge a premium for that efficiency, but it is prevented from getting too big for its britches because its Tile processors are not compatible with the x64 instruction set and require companies to port and certify their software to run upon them.

When pressed about its future pricing strategy, Bishara says that the Tile-Gx 3036 "will be competitive with the eight-core Sandy Bridge chip," and adds that Tilera "needs to be competitive with Intel on price so that means we need to at least match them". ®