This article is more than 1 year old

Intel readying MIC x64 coprocessor for 2012

Knights Corner not just around the corner

On boards with Knights Ferry

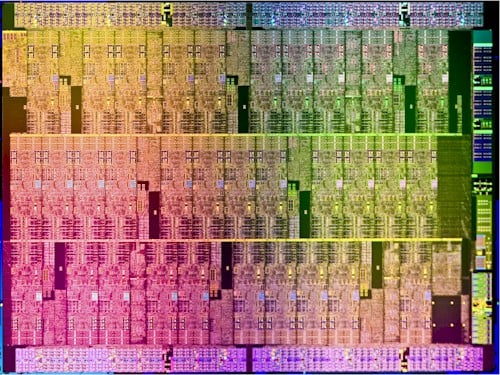

The Knights Ferry software development platform is based on a 32-core MIC design code-named "Aubrey Isle," shown below:

The Aubrey Isle chip is implemented using Intel's 45 nanometer processes and puts 32 cores running at 1.2GHz on the die; each core has four instruction threads, given 128 execution threads per die.

The chip has 8MB of shared L2 cache plus either 1GB or 2GB of GDDR5 graphics memory. (Yes, it is a graphics card, even if Intel says it isn't, although good luck trying to find a video driver for it.) Each core has 32KB of L1 instruction and 32KB of L1 data cache, and the cores can talk to the GDDR5 memory through PCI direct memory access operations with virtual addressing.

As for the production chip, all Intel has said, and which it reiterated for the ISC briefing, is that the future Knights Corner coprocessor would have more than 50 cores and would use the 22 nanometer process. The rumored delivery for the chip is the second half of 2012, which means Knights Corner follows Ivy Bridge PC and server chips and probably Poulson Itaniums, too.

If I had to guess, I would say that the chip used in the Knights Corner coprocessor will have 64 cores and vector units on a ring interconnect – or perhaps multiple rings within rings – and that the number of activated cores and vectors will depend on how many bits of gunk kill off computing units on a chip as the 22 nanometer processes ramp.

This is perfectly normal in the GPU space. For instance, with the Fermi GPUs from Nvidia, the design has 512 cores, but the first year of shipments for the M2050 and M2070 units had GPUs with only 448 cores working; only with the just-announced M2090s and the future X2090s (for embedding right onto server system boards) are all 512 cores working. Similarly, CPUs that are designed with a high number of cores are sold with SKUs with fewer cores because of boogers on the chips; using these semi-dud chips increases yields and hurts no one.

PCI today, on-package tomorrow

Intel is not confirming if the Knights Corner coprocessor will plug into servers using the PCI-Express 2.0 interface or the faster PCI-Express 3.0 interface that will initially debut in the third quarter of this year with Intel's "Sandy Bridge" Xeon E5 processors and Advanced Micro Devices' "Interlagos" Opteron 6200s.

Intel could go either way – or both ways depending on what prospective customers are telling it. The PCI bus is the bottleneck for coprocessors and networks alike at this point, so you have to believe that Intel is tempted to only support PCI-Express 3.0 slots given the low volume of MIC coprocessors it will ship and its desire to pair these with Sandy Bridge server upgrades.

Over time, it is perfectly reasonable to expect that Intel will package up a Knights coprocessor on the chip package, or perhaps on the die itself, for its HPC customers. It has to do something with all of those transistors on future 14 nanometer processes after all.

Neal-Graves said that Intel initially had 10 partners helping it work with the Knights Ferry development platform last year, and ramped that up to 25 partners by the end of 2010. By the end of June, the plan is to have 50 partners, and the goal is to expand that to 100 by the end of this year.

At the ISC event in Hamburg, Germany, this week, Intel is showing off servers and workstations using the Knights Ferry development platform, working with Silicon Graphics, Hewlett-Packard, IBM, Dell, Super Micro, and Colfax International.

The Forschungszentrum Juelich (FZJ) and Leibniz Rechenzentrum (LRZ) labs in Germany, Centre Européenne pour la Recherche Nucléaire (CERN) in Switzerland, the National Center for Supercomputing Applications (NCSA) in the United States, and the (Korea Institute of Science and Technology Information in South Korea are all playing around with prototype Knights Ferry machines, testing their codes.

In one test, Colfax took one of its CXT8000 servers with two Intel Xeon X5690 chips (six cores running at 3.46GHz) and slapped in 24GB of memory and eight of the Knights Ferry coprocessors with the chips running at 1.2GHz. Using the Larrabee 1.6.197 kernel driver (see, it really is a Larrabee GPU), this 4U rack server was able to deliver 7.4 teraflops running the aforementioned SGEMM sorting benchmark. This was using alpha levels of future compilers and drivers from Intel.

Intel is not talking about the performance of the Knights Corner coprocessors, but if you do the math, a chip with somewhere between 50 and 64 cores running at between 1.2GHz and 1.5GHz should get you around 1 teraflops at single precision floating point math and half that on double precision. Crank it up to 2GHz, which the 22 nanometer process should allow before flames shoot out of the device, and then a 64-core MIC coprocessor gets you 2 teraflops single precision and the magic 1 teraflops at double precision, we estimate. ®