This article is more than 1 year old

Tilera to stuff 200 cores onto single chip

Plus memory, controllers, mesh network...

Coming soon: 40,000 core rack

As El Reg has previously reported, supercomputer maker Silicon Graphics has committed to putting a petaflops of computing into a single rack under its Project Mojo effort, and has mumbled a bit about supporting various architectures, including Tilera processors, as part of that effort. It would be very interesting to see SGI pair Tilera processors with GPU co-processors to get there.

And it looks like this could work. Bishara says that the long-awaited third generation of Tile processors, announced last October are making their way through qualification. These Tile-Gx processors are being implemented in a 40 nanometer process at TSMC's wafer bakers and will sport 64-bit cores and floating point math.

The Tile-Gx family will run at between 1 GHz and 1.5 GHz, thanks to the process shrink, and will come in versions with 16, 36, 64, and 100 cores. The Tile-GX16 and Tile-GX36 processors will have 16 and 36 cores, as their names suggest, and will start sampling to customers in the fourth quarter with production volumes one or two quarters later, according to Bishara. The larger Tile-Gx64 and Tile-Gx100 processors will sample in the second quarter of 2011 and will be in production in either the third or fourth quarter if all goes according to plan.

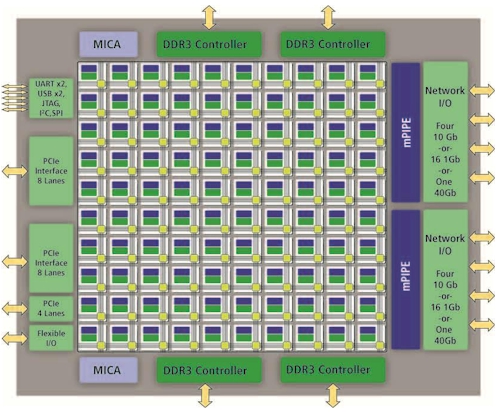

The Tile-Gx100 processor will have four DDR3 memory controllers on its SoC grid (a 10x10 layout) and will be able to address 1 TB of main memory. This will represent a big bump up in performance – about 8X the oomph compared to the Tile64Pro being used by Quanta in the SQ2 server – and a factor of 32X increase in main memory. The Tile-GX100 SoC will have three PCI-Express controllers (with a total of 20 lanes) running down the left side of the chip, plus controllers for other I/O devices. The right side of the chip will have two network I/O controllers, each capable of supporting sixteen Gigabit Ethernet ports, four 10 Gigabit Ethernet ports, or a single 40 Gigabit Ethernet port. Here's the block diagram of the Tile-GX100:

With the Tile-Gx generation of chips, Tilera says that its server partners will be able to cram around 20,000 cores in a rack (with more performance than the current cores), and with a fourth generation of chips code-named "Stratton," due in 2013 using a 28 nanometer process from TSMC, it will be possible to do double that again to around 40,000 cores. Bishara did not say what other architectural changes were coming with the fourth generation, but you can bet it will be something interesting. ®